本文來自:半導體行業觀察

從英特爾悄悄拿起,

到臺積電發揚光大,

再被三星輕輕放下,

FinFET登臺已10年之久,

如今隨着摩爾定律逐漸失速,

新的時代迎來新的繼承者。

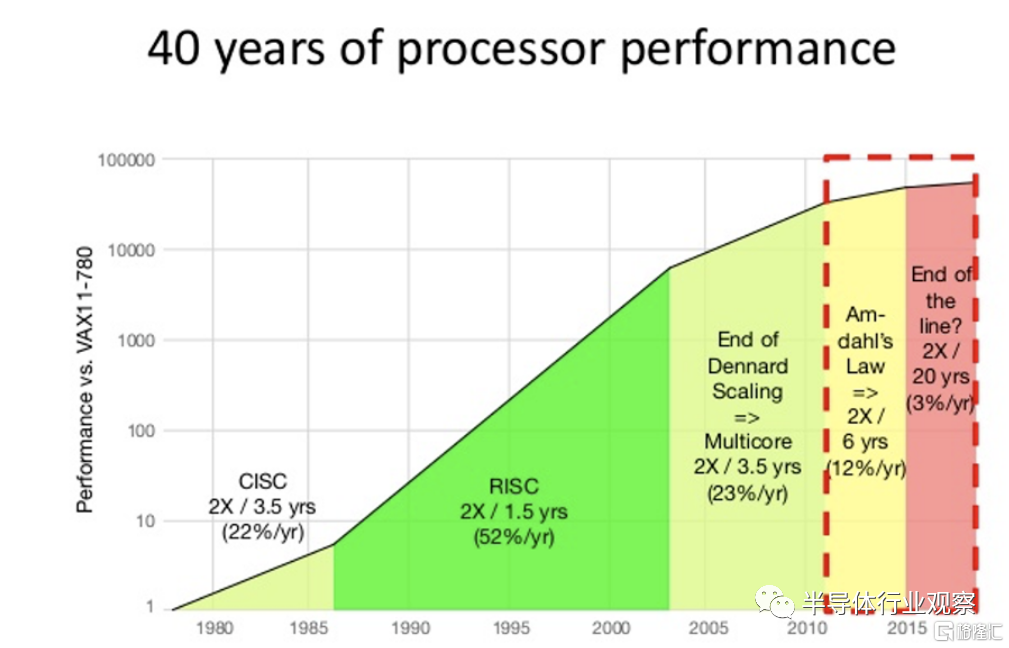

40年來處理器性能變化(圖源:CAOS)

近日,據eenews消息,三星代工廠流片了基於環柵 (GAA) 晶體管架構的3nm芯片,通過使用納米片(Nanosheet)製造出了MBCFET(多橋通道場效應管),可顯著增強晶體管性能,主要取代FinFET晶體管技術。

該工藝需要一套不同於FinFET晶體管結構的設計和認證工具,因此三星使用了Synopsys的Fusion Design Platform。該工藝的物理設計套件(PDK)於2019年5月發佈,並於去年通過了認證。伴隨着此次成功流片,意味着三星3nm芯片大規模量產的時間點已正式臨近。

三星執行副總裁兼代工銷售和營銷主管Charlie Bae表示:“基於GAA結構的下一代工藝節點(3nm)將使三星能夠率先打開一個新的智能互聯世界,同時加強我們的技術領先地位”。

什麼是GGA?

GGA——(Gate all around Field Effect Transistors,GAAFET),又稱全環柵晶體管,是一種繼續延續現有半導體技術路線的新興技術,可進一步增強柵極控制能力,克服當前技術的物理縮放比例和性能限制。

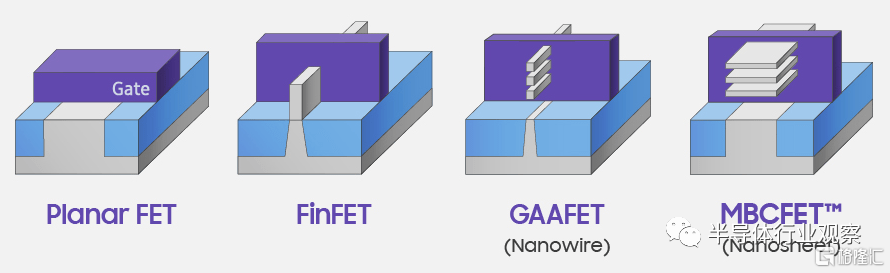

據瞭解,GAAFET有兩種結構,一種是使用納米線(Nanowire)作爲電子晶體管鰭片的常見GAAFET,另外一種則是以納米片(Nanosheet)形式出現的較厚鰭片的多橋通道場效應管MBCFET,這兩種方式都可以實現3nm,但取決於具體設計。從GAAFET到MBCFET,可以視爲從二維到三維的躍進,能夠改進電路控制,降低漏電率。

按照專家觀點:GAA晶體管能夠提供比FinFET更好的靜電特性,可滿足某些柵極寬度的需求。這主要體現在同等尺寸結構下,GAA溝道控制能力增強,給尺寸進一步微縮提供了可能;傳統FinFET的溝道僅三面被柵極包圍,而GAA以納米線溝道設計爲例,溝道的整個外輪廓都被柵極完全包裹住,意味着柵極對溝道的控制性能就更好。

Leti公司高級集成工程師Sylvain Barraud指出:“與FinFET相比,除了具有更好的柵極控制能力以外,GAA堆疊的納米線還具有更高的有效溝道寬度,能夠提供更高的性能。”

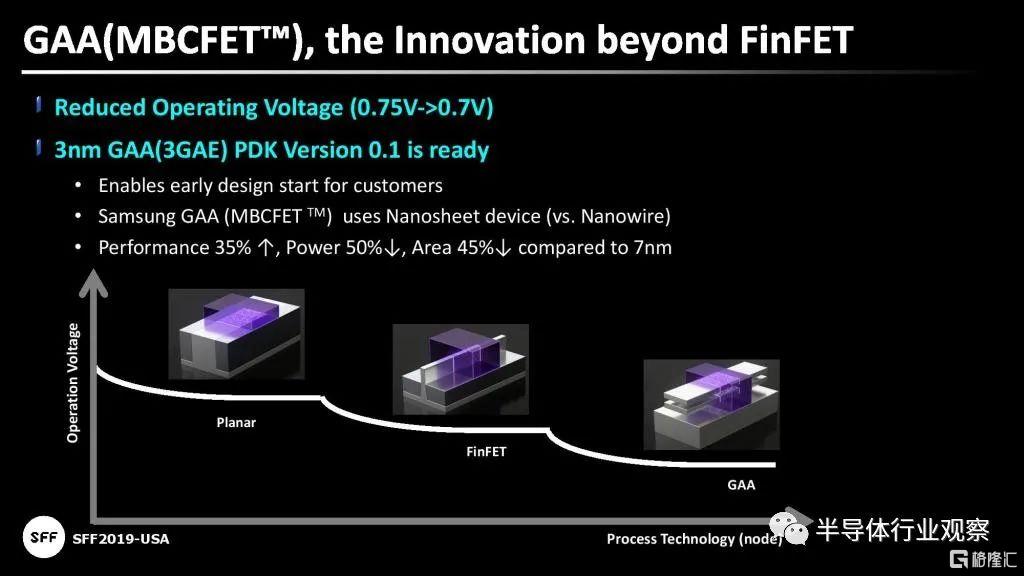

GAA相比FinFET的優勢(圖源:semianalysis)

根據三星的說法,與7nm FinFET製造工藝相比,3nm GAA技術的邏輯面積效率提高了35%以上,功耗降低50%,邏輯面積減少45%。

能夠看到,GAA晶體管結構標誌着工藝技術進入了關鍵轉折點,對於保持下一波超大規模創新所需的縮放軌跡至關重要。

三星和臺積電的岔路口

目前,臺積電、三星在5nm/7nm工藝段都採用FinFET結構,而在下一世代3nm工藝的晶體管結構選擇上,兩者出現分歧。

三星選擇採用GAA結構。在今年的IEEE國際固態電路大會(ISSCC)上,三星首次公佈了3nm製造技術的一些細節——3nm工藝中將使用類似全柵場效應晶體管(GAAFET)結構,率先開啓了先進工藝在技術架構上的轉型。

臺積電則出於穩健考慮,選擇在第一代3nm工藝繼續沿用FinFET技術,儘可能實現無縫過渡。畢竟在相同的製程技術與製造流程下,不用變動太多的生產工具,也能有較具優勢的成本結構。尤其是對客戶來說,在先進製程的開發裏變更設計,無論是改變設計工具或者是驗證和測試的流程,都會是龐大的時間和經濟成本。臺積電首席科學家黃漢森強調,做此選擇是從客戶的角度出發,採用成熟的FinFET結構產品性能顯然會更加穩定,也有助於客戶降低生產的成本。

不過,這或許只是一個短期策略。依託FinFET技術,臺積電芯片工藝製程的終點來到了3nm,當鰭片(Fin)寬度達到5nm(等於3nm節點)時,FinFET將接近實際極限,再向下就會遇到瓶頸。

因此也有消息透露,臺積電的2nm工藝將轉向GAA架構(採用跟三星一樣的MBCFET架構)。全新的MBCFET架構,以GAA製程爲基礎的架構,可以解決FinFET因爲製程微縮而產生的電流控制漏電等物理極限問題。

平面晶體管與FinFET、GAAFET以及MBCFET(圖源:Semianalysis)

綜合來看,2nm或將是FinFET結構全面過渡到GAA結構的技術節點。在經歷了Planar FET、FinFET後,晶體管結構將整體過渡到GAAFET結構上。

三星和臺積電的選擇考量都是商業決策下的結果。對臺積電和客戶來說,維持當前的設計體系,擴展FinFET似乎是一條更安全的途徑。若最終的產品性能還能與競爭對手平起平坐,那臺積電可能又將在3納米產品世代再勝一籌。

對三星來講,3nm時代在技術架構方面尋找差異化,試圖進一步拉近與臺積電芯片代工方面的技術差距。IBS首席執行官Jones表示:“與3nm FinFET相比,3nm環繞閘極具有更低的閾值電壓,並可能降低15%到20%的功耗,在某種程度上提供了更多的性能。”三星正在通過新的嘗試和提前佈局來尋求更多可能性。

FinFET走到了盡頭?

過去十年,FinFET技術成功延續了摩爾定律,但時至今日,隨着摩爾定律失速,FinFET也彷彿走到了盡頭。

談到FinFET,得從平面MOSFET開始說起,自平面MOSFET器件工藝誕生後,特徵尺寸就隨着摩爾定律的指引在不停地縮小。在晶體管特徵尺寸微縮的過程中,雖然也遇到過各種困難,但是通過將鋁互聯改成銅互聯,在柵極加入High-k材料、引入Stress engineering等方法都可以在不改變平面器件工藝的情況下把尺寸做小。

但是當柵極長度逼近20nm門檻時,對電流的控制能力急劇下降,漏電率也在升高,傳統的平面MOSFET看似走到了盡頭,材料的改變也無法解決問題。

對此,加州大學伯克利分校胡正明教授給出了新的設計方案,也就是FinFET晶體管,又稱鰭式場效應晶體管。在FinFET中,溝道不再是二維的,而是三維的“鰭(Fin)”形狀,而柵極則是三維圍繞着“鰭”,這就大大增加了柵極對於溝道的控制能力,從而解決漏電問題。

胡正明教授2001年在學界正式提出FinFET方案,但真正被商業落實還是在十年以後。英特爾在FinFET工藝上率先出手,2011年推出了商業化的22nm FinFET工藝技術。隨後包括臺積電在內的全球各大半導體廠商積極跟進,陸續轉進到FinFET工藝中。從16/14nm開始,FinFET成爲了半導體器件的主流選擇,成功地推動了從22nm到5nm等數代半導體工藝的發展,並將擴展到3納米工藝節點。

FinFET工藝七大玩家進展(圖源:芯思想)

FinFET工藝技術自2011年商業化後,體系結構持續進行改進,以提高性能並減小面積。到了5nm節點後,雖然使用了EUV光刻技術,但是基於FinFET結構進行芯片尺寸的縮小變得愈發困難。FinFET工藝製造、研發成本也越來越高,即使在7nm、5nm仍能堅持,但是再往前似乎已經是力不從心。

隨着三星、英特爾兩大晶圓代工巨頭率先轉向GAA工藝,正在預示着在更先進的節點上,FinFET將走向終結。根據國際器件和系統路線圖(IRDS)的規劃,在2021-2022年以後,FinFET結構將逐步被GAA結構所取代。

然而,雖然FinFET無法再繼續深耕更先進的工藝節點,但在現有業務佈局中仍佔有相當份額,並正處於逐年增長的態勢。這一點從臺積電FinFET工藝收入中能夠得到印證。

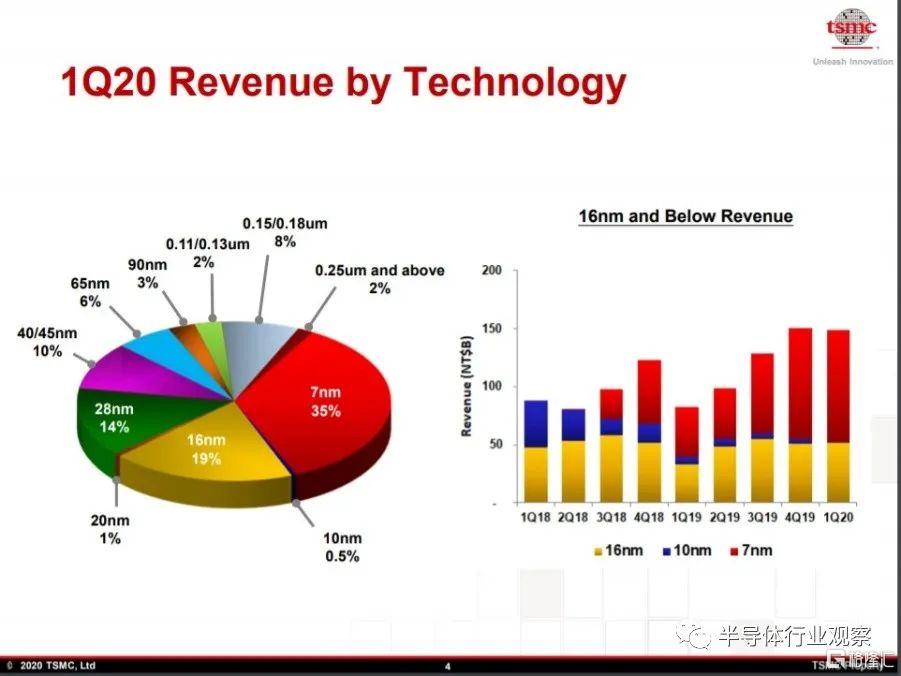

圖源:TSMC

從上面數據可以看到,臺積電2020年第一季度FinFET工藝收入佔比54.5%,在2021年第一季度更是達到驚人的63%。FinFET收入增長背後,離不開臺積電在此的專注和投入,在當前半導體短缺的情況下,臺積電3年投資1000億美元建設大量的FinFET產能,應對市場和客戶需求。同時,臺積電正在努力推動其500多個客戶進入FinFET時代,加速其繁榮。

因此,現在說FinFET壽終正寢還爲時尚早,臺積電正在將FinFET帶向多個領域。

芯片製造的未來走向

市場對於高性能芯片的渴望在不斷推動技術的演進,在人們爲3nm節點工藝擔憂的時候,新的GAA技術出現了。那麼除此之外,芯片製造未來還有哪些走向?

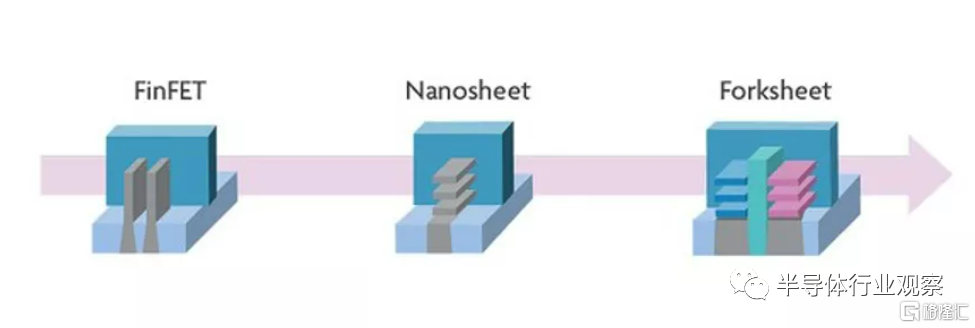

Forksheet FET & CFET

隨着未來向更小製程的繼續,將要求標準單元內nFET和pFET器件之間的間距更小。但是,對於FinFET和Nanosheet而言,工藝限制了這些n-to-p器件之間的間距。

除了Nanosheet,還有一些屬於“全柵”類的其它技術選項。爲了擴大這些器件的可微縮性,IMEC提出了一種創新的架構,稱爲Forksheet FET。

Forksheet被視爲下一個發展路線(圖源:IMEC)

Forksheet可以理解爲是Nanosheet的自然延伸,具有超出2nm技術節點的額外縮放和性能。Forksheet的nFET和pFET集成在同一結構中,由介電牆將nFET和pFET隔開。這個技術的優勢就在於它有更緊密的n到p的間距,並減少面積縮放。與Nanosheet FET相比,在相同製程下,Forksheet FET的電路更加緊湊。

在從平面晶體管到FinFET再到Nanosheet的進化過程中,可以將Forksheet視爲下一個發展路徑。

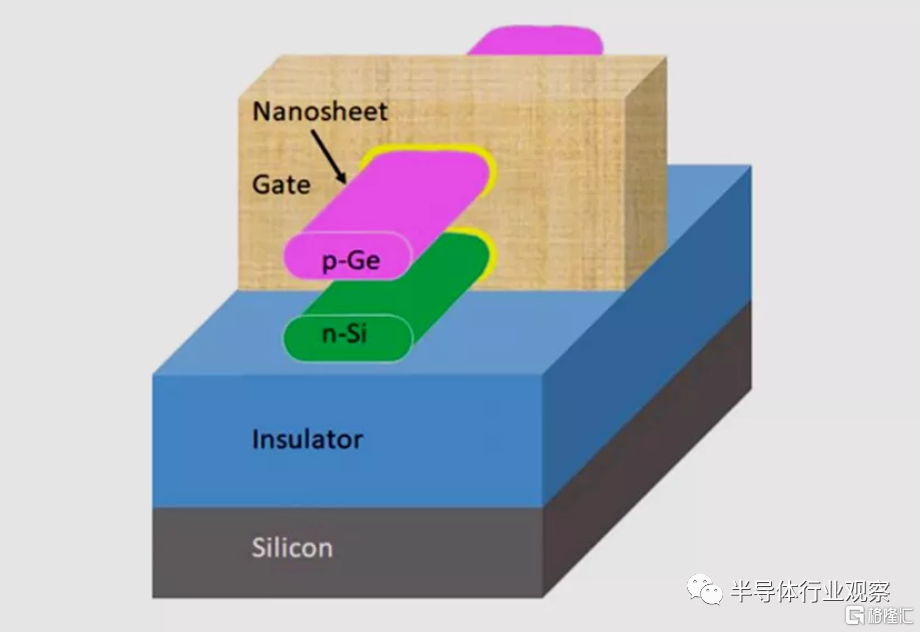

此外,CFET——Complementary FETs(互補場效應晶體管)是2nm甚至以後另一種類型的技術選項。CFET由兩個獨立的Nanosheet FET(p型和n型)組成,是一種把p型納米線疊在n型納米線上的結構。通過這種疊加的形式,CFET等於是實現了一種摺疊的概念,藉此消除了n-to-p分離的瓶頸,能夠將單元有源區域的面積減少2倍。

CFET結構

IBS首席執行官Handel Jones稱:“CFET前景廣闊,但目前還爲時過早。向1nm CFET系列邏輯器件的發展推動了新BEOL和MOL解決方案的開發,但問題是即使增強了柵極結構,我們也需要增強MOL和BEOL,需要通過引入新的導體來補充這些集成方案,否則性能提升將受到限制。”

對於未來技術架構的演進趨勢,IMEC認爲:3納米之前採用Nanosheet、2納米採用Forksheet、1納米採用CFET。在進一步的研究中,需要解決將這些器件完全投入生產的工藝挑戰。

總而言之,目前這些仍在研發中的技術前景尚好,但也都有更自的挑戰待突破,包含散熱的控制和製造成本等,但可以看到的是,對於2納米及之後的芯片製造,已有數項技術正在進行中,雖有困難但也是遙不可及。

Bizen晶體管架構

英國初創公司Search For The Next(SFN)和蘇格蘭芯片製造商Semefab合作開發了Bizen晶體管架構,可能從另一方向打破CMOS的極限。提出Bizen晶體管架構最初的目的就是爲了創建具有較少掩膜步驟的芯片,使得同一塊芯片上同時具有邏輯和功率晶體管,在這一初衷下創建一個LED驅動器的集成電路。

SFN首席執行官Summerland提出了使用齊納二極管反向偏置特性的想法,該特性是由二極管N區域和P區域之間摻雜水平的突然變化產生的,最終致使量子電流的產生,以此來驅動雙極晶體管。

具體而言,SFN的Bizen晶體管設計將雙極結與齊納二極管的概念結合在一起,利用量子隧穿效應從傳統的雙極晶體管中消除了電阻以及所有金屬層。晶體管使用量子隧道連接柵極並能夠建立多個柵極連接,這意味着可以在一個晶體管內創建多個非門和或門,從而縮小了邏輯電路的裸片。

半導體材料:鉍(Bi)

從材料方面來看,目前硅基半導體主流製程已進展至5nm、甚至3nm的節點,芯片單位面積能容納的電晶體數目,也將逼近硅的物理極限,芯片效能無法再逐年顯著提升。

一直以來業界對二維材料寄予厚望,卻苦於無法解決二維材料高電阻、及低電流等問題,前不久,由臺大、臺積電與麻省理工學院(MIT)共同發表的研究表示,由美國麻省理工團隊發現在二維材料上搭配半金屬鉍(Bi)的電極,能大幅降低電阻並提高傳輸電流。隨後臺積電技術研究部門將鉍(Bi)沉積製程進行優化,臺大團隊並運用氦離子束微影系統(Helium-ion beam lithography)將元件通道成功縮小至納米尺寸,終於獲得這項突破性的研究成果。

臺大電機系暨光電所吳志毅教授進一步說明,使用鉍(Bi)爲接觸電極的關鍵結構後,二維材料電晶體的效能不但與硅基半導體相當,又有潛力與目前主流的硅基製程技術相容,有助於未來突破摩爾定律的極限。

半導體設備:EUV的下一步

從DUV到EUV的過渡對延續摩爾定律起到了重要作用。爲了繼續微縮,幾年前ASML開始研發下一代工具——High NA(高數值孔徑)EUV,提升NA(numerical aperture,鏡口率 ) 的基礎上進一步提高半導體微細加工所需的電路分辨率。

ASML預計,High NA設備將在2025年或2026年進入商業生產。與傳統的EUV光刻相比,High NA EUV光刻有望提供更先進的圖案縮放解決方案。此外,在未來的工藝節點上,除了下一代EUV光刻技術外,新的沉積,蝕刻和檢查/計量技術也在研究中。

寫在最後

3nm即將發生,2nm也是如此。由於沒有一種技術可以滿足所有的應用,在芯片縮小和功能擴展的過程中,製程的進步、晶體管結構的變化和其他方法會交替進行,不斷推動芯片性能向上攀升

在此情況下,除了製造商需要各顯本事之外,如何從技術、市場與成本中取得最大的利基,將是個企業間競爭的關鍵所在。特別是先進半導體制造的成本十分高昂,若不能在生產技術與製造成本中取得較佳的平衡,未來發展也將會非常艱辛。再考慮到半導體制造供應鏈龐大的牽連體系,不僅是製造設備,也包含設計工具和檢驗測試等部分,若沒有優異的解決方案,也難以在競爭中保持優勢地位。

在寫下這篇文字的時候,前方又傳來消息:“三星圍繞3nm節點進行了大量營銷和炒作,目前看起來形勢嚴峻,產品性能似乎也進行了大量修改,基於GAA架構的3nm節點預計將推遲到2024年推出...”

但貌似也無傷大雅,2022年也好,2024年也罷。

不難預見,屬於GAA晶體管的時代正在開啓...