臺積電出新招

本文來自格隆匯專欄:半導體行業觀察,作者:暢秋

臺積電要在5nm及更先進製程保持領先,EUV光刻機是重要一環,近年來,該公司不斷購入EUV設備,以維持先進製程產能優勢。臺積電於日前召開技術論壇,指出其EUV設備累計裝機數量到2020年已佔全球總數的50%,到2020年爲止,採用臺積電EUV技術生產的晶圓,佔全球EUV光刻晶圓數的65%。而隨着製程推進至5nm,每片晶圓採用EUV掩模層大幅拉昇,臺積電預估2021年EUV掩模產能將是2019年的20倍。

今年下半年,臺積電5nm產能進一步提升,包括蘋果A15應用處理器及M1X/M2計算機處理器、聯發科及高通新款5G手機芯片、AMD Zen 4架構計算機及服務器處理器等將陸續導入量產。臺積電爲了維持技術領先,由5nm優化後的4nm將在明年進入量產,全新3nm也將在明年下半年導入量產。

下面具體看一下這些需要用到EUV設備的先進製程情況。

臺積電5nm於2020年量產,2023年,包括4nm的5nm系列製程產能將會比2020年大幅增長4倍。此外,臺積電還推出了5nm家族的最新成員-N5A製程,目標在於滿足汽車應用對於運算能力日益增加的需求。

位於臺南的晶圓18廠第1、2、3、4期是5nm生產基地,其中,第1、2、3期已經開始量產,4期興建中。

5nm家族中的4nm加強版由於減少了掩模層數,以及與5nm幾近兼容的設計法則,進一步提升了效能、功耗效率、以及晶體管密度。4nm工藝將把芯片尺寸收縮 6%,同時帶來功耗和性能上的進一步改善。

3nm方面,將增加EUV的使用量,效能將比5nm提升10-15%,功耗減少25-30%,邏輯密度增加1.7倍,SRAM密度提升1.2倍、模擬密度則提升1.1倍。

2nm方面,臺積電將在新竹市新建一座 Fab 20 工廠,用於2nm系列製程工藝的生產。儘管當前仍在忙着徵地,但該公司已經爲 Fab 20 工廠的初期生產規劃了四個階段。

隨着以上最先進製程晶圓廠在未來1~3年內逐步完成建設並投入量產,以及美國亞利桑那州12吋廠第一期在2024年後進入量產,採用臺積電EUV技術的晶圓數將快速增長,其在EUV設備上的投資將越來越大。

01

對手虎視眈眈

目前,作爲臺積電在先進製程領域的唯一對手,三星一直在努力追趕中,這給臺積電帶來了不少壓力,無論是技術層面,還是在成本層面,都需要不斷優化,才能保持對三星的優勢。

三星預計2021年將在半導體設施上投資35萬億韓元,創歷史新高,比2020年的28.9萬億韓元增長20%。股票分析師預計,該公司將在存儲芯片上花費24萬億韓元,在系統半導體上花費11萬億韓元。

三星不僅將在韓國投資,還將在美國和中國投資。在韓國,其在平澤的工廠將轉變爲存儲器和系統半導體的生產基地。晶圓代工生產線於今年年初投入使用,預計將於下半年開始運營。此外,預計該公司將在2021年完成3號工廠的建設,該工廠將生產內存和晶圓代工產品。

另外,三星還計劃在美國投資170億美元建設新晶圓廠,用於生產5nm及以下先進製程芯片。這主要針對的就是臺積電在美國的5nm新廠。

三星擴建最先進製程晶圓廠,同樣需要大量的EUV設備。爲此,不久前,韓國總統文在寅和荷蘭首相馬克·呂特舉行了虛擬峯會,期間,關於與ASML的深入合作是一項重要議題。雙方的聲明中寫道:“兩國同意加強在半導體供應鏈方面的合作,相互承認對方是半導體領域的核心合作夥伴。”

對於尋求在全球半導體競賽中保持領先地位的韓國芯片製造商,特別是三星來說,ASML的EUV設備至關重要。三星電子副董事長李在鎔去年 10 月訪問了ASML,顯然是爲了獲得 ASML的EUV光刻機。

5月,ASML與韓國中央和地方政府簽署了一份諒解備忘錄,將投資 2400 億韓元(2.111 億美元),到 2025 年在京畿道華城建立 EUV 產業集羣。

據日本專家分析,2020年,當5nm大規模生產及3nm試產啓動時,臺積電需要35臺新EUV光刻機。到2021年,5nm生產規模擴大,3nm風險生產將啓動,所需的新EUV光刻機數量達54臺;到2022年,當3nm大規模生產、2nm試產啓動,需要的新EUV光刻機數量爲57臺。

三星方面,李在鎔在2020年訪問ASML期間要求的“2020年9臺EUV光刻機”中,至少有4臺將2020年抵達三星,其餘5臺在2021年初引入。尚不清楚2021年後是否會落實每年20臺EUV設備,但實際數字相差不會很大。

根據假設得出的結論,臺積電在2021-2015年間總共需要292臺EUV光刻機,每年平均需新增58臺。三星每年需要20臺,一共需要近80臺。這將是一筆龐大開支。

02

臺積電壓力山大

對於臺積電來說,雖然其先進製程,特別是5nm目前無敵於天下,但客戶對於使用4nm或全新3nm態度還不夠明朗,主要原因是成本太高,而其決定因素是EUV掩模層數不斷增加,再加上EUV設備本身就是高成本,兩個因素疊加,直接提升了晶圓代工價格。

由於先進製程投資金額愈來愈高,能夠支付如此龐大晶圓代工費用的半導體廠已經沒有幾家,雖然臺積電現在有蘋果、NVIDIA、AMD、高通、聯發科、英特爾、博通、Marvell、賽靈思(Xilinx)等大客戶採用先進製程,但隨着三星晶圓代工積極擴產,英特爾加碼先進製程產能投資,臺積電面臨的競爭壓力越來越大。

爲了在明年之後加速客戶5nm產品線轉換至3nm,據悉,臺積電將啓動EUV持續改善計劃(Continuous Improvement Plan,CIP),希望在略爲增加芯片尺寸的同時,減少先進製程EUV掩模使用層數,以降低3nm成本。

EUV光刻機價格越來越高,ASML在下半年即將推出的最新機型NXE:3600D,其價格高達1.4~1.5億美元,產出吞吐量每小時可達160片12吋晶圓,與上代機型相比,產能增加幅度不大。而由製程來看,4nm由5nm優化而來,EUV掩模層大約在14層以內,但3nm預計將採用25層EUV掩模,因此,3nm晶圓代工價格恐怕會達到3萬美元,並不是所有客戶都願意買單。

爲了加快客戶產品線由5nm向3nm的推進速度,臺積電啓動EUV CIP計劃改善製程,希望透過減少EUV掩模層使用道數及相關材料,例如將3nm的25層EUV掩模層減少至20層,雖然芯片尺寸將因此略爲增加,但若計劃成功可以有效降低生產成本及晶圓價格。若能有效減少3nm晶圓EUV掩模層數,在達成同樣產出量情況下將有助於減少EUV設備採購量,若每年少採購1~2臺EUV設備,資本支出也可降低3億美元。

臺積電的成本壓力,從最近發佈的第二季度財報也可見一斑。其單季稅後純益 1343.6 億元新臺幣,季減 3.8%,年增 11.2%,每股純益 5.18 元,低於市場預期。第二季營收 132.9 億美元,季增 2.9%,年增 28%,毛利率 50%,季減 2.4 個百分點,年減 3 個百分點,營益率 39.1%,季減 2.4 個百分點,年減 3.1 個百分點;稅後純益 1343.6 億元,季減 3.8%,年增 11.2%。

另外,上半年營收 262.08 億美元,新臺幣營收 7345.55 億元,年增 18.2%,毛利率 51.2%,年減 1.2 個百分點,營益率 40.3%,年減 1.5 個百分點。

總體來看,營收增長,但利潤下降了,這其中很重要的原因就是在先進製程上的投資巨大,難以被營收抵消。

以製程來分,臺積電第二季 5 nm製程出貨佔晶圓銷售金額的18%,7 nm爲 31%,16 nm爲 14%,28 nm爲 11%。可見,5nm佔比很大,僅次於7nm,這同時說明其需要在這方面投入巨資,才能實現這樣的量產水平,但相應的回報與投入並不呈線性關係。

基於以上這些因素,臺積電要想繼續發展最先進製程,同時保持競爭力,不至於內對手縮小差距,就必須在成本控制方面多下功夫了。

03

多渠道降本增效

除了減少EUV光刻機採購數量及掩模層數外,還可以有多種方法降低最先進製程的成本,同時保證良好的性能。

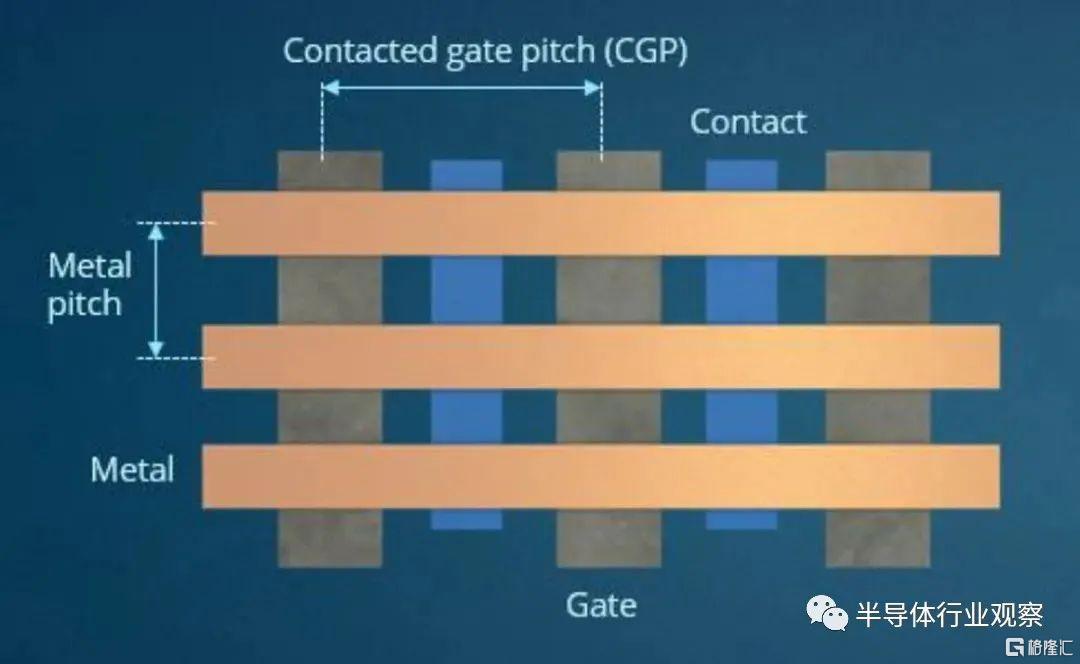

例如,可以通過設計和技術協同優化(DTCO)減少器件佔用空間。邏輯器件是許多邏輯單元的組合,這些邏輯單元執行基本邏輯功能。每個單元都具有多個晶體管柵極,這些晶體管柵極由金屬線連接。垂直排列的門之間的距離稱爲接觸門間距(CGP)。水平連接柵極的金屬線之間的距離稱爲金屬間距。通過乘以兩個間距,可以估計單元單元的一個區域。

傳統上,業內使用光刻圖案來精細化柵極和導線,通過更緊湊的方式縮放,這稱爲內在縮放。但是,隨着製程節點的推進,進一步縮短柵極和導線距離的物理空間正在迅速消失。此外,如果電氣器件和結構太密集,信號可能會幹擾,從而降低器件的性能和功率特性。

設計與技術的協同優化(DTCO)可實現與以往不同的縮放技術,這被視爲未來節點的總體縮放優勢,因此備受關注。其旨在將新材料和材料工程技術與邏輯設計師的出色理念相結合,在不改變光刻或間距的情況下降低每個區域的成本。

DTCO 是一種從設計和技術兩方面進行優化的方法。利用DTCO,可將更多的功能塞進邏輯單元的有限區域。

爲了在提高 PPAC(功耗、性能和每面積成本)的同時實現可靠性和產量,必須保持邊緣的線性度和平滑度。事實上,任何圖案形狀在邊緣上通常都會發生粗糙度和不均勻性,但傳統上,由於邊緣在圖案線寬中所佔的比例非常小,因此這種擾動基本上可以忽略不理。但是,隨着 EUV 縮放的推進,邊緣佔據線寬 30% 的情況並不少見。邊緣粗糙度是一個嚴重的問題。光刻分辨率和線邊緣粗糙度問題愈加突出。

目前,創新的集成材料解決方案正在出現,這些解決方案在納米級響應這些挑戰,併成功地實現 EUV 雙圖案化。

總之,使用DTCO 可以繼續推進先進製程,同時提高PPAC。

04

結語

當製程發展到3nm,臺積電這樣的龍頭企業也對成本愈加敏感,需要採取有效方法把成本降下來,除了以上提到的幾點方法之外,產業鏈上下遊廠商也在探索更多、更好的方法,以求將摩爾定律繼續推進下去。